Samsung починає виробництво чипів на базі 3-нм техпроцесу з архітектурою Gate-All-Around

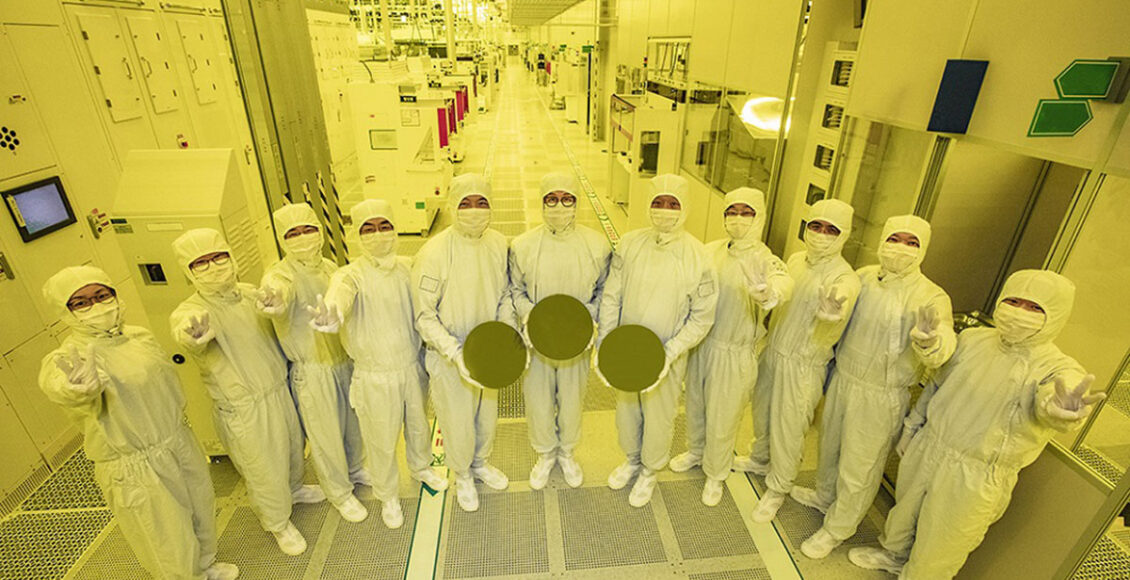

Компанія Samsung Electronics оголосила про початок виробництва чипів на базі свого 3-нанометрового технологічного вузла із застосуванням архітектури транзисторів Gate-All-Around (GAA).

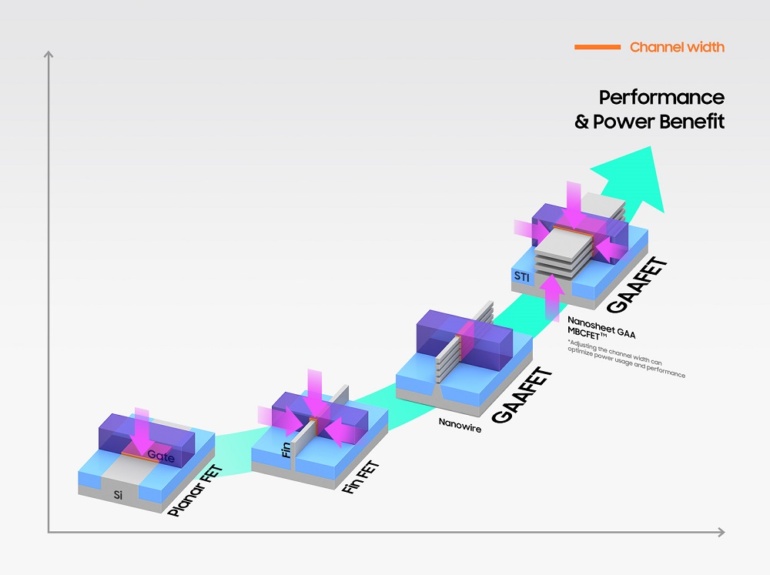

Зазначимо, що архітектура GAAFET, що йде на зміну нинішній FinFET, розробляється організацією, до якої входять IBM, Globalfoundries і Samsung, з 2000 року. Вона має допомогти подолати фізичні обмеження щодо масштабування МОП. Головна особливість GAAFET – кільцеві затвори (звідси й назва gate-all-around FET). Канали транзисторів GAAFET є нанопроводами (вони сформовані з декількох горизонтальних кремнієвих «нанолистів»). Водночас канал FinFET транзистора під затвором є монолітною вертикальною конструкцією «плавник», що і накладає обмеження по масштабуванню.

Samsung має власну реалізацію технології GAAFET, яка має маркетингову назву Multi-Bridge-Channel FET (MBCFET). Насправді MBCFET відрізняється від GAAFET не лише назвою, а й технічно: у разі реалізації Samsung канали виконані у вигляді плоских «містків», а не «проводків».

Як заявляють у Samsung, технологія MBCFET долає обмеження продуктивності FinFET, підвищуючи ефективність енергоспоживання шляхом зниження рівня напруги живлення, а також збільшуючи продуктивність внаслідок збільшення допустимого струму приводу. У запатентованій технології Samsung використовуються нанолісти з ширшими каналами, що забезпечує підвищену продуктивність та більшу енергоефективність у порівнянні з технологіями GAA, які використовують нанопроводки з вужчими каналами. Використовуючи 3-нм технологію GAA, Samsung зможе регулювати ширину каналу наноліста, щоб оптимізувати енергоспоживання та продуктивність для задоволення потреб клієнтів.

Нова технологія використовуватиметься для виробництва напівпровідникових чипів для високопродуктивних обчислювальних додатків з низьким енергоспоживанням і планує розширити її на мобільні процесори.

Зазначається, що оптимізований 3-нм техпроцес забезпечує зниження енергоспоживання на 45%, підвищення продуктивності на 23%, а також меншу площу поверхні кристала на 16% в порівнянні з 5-нм техпроцесом.

Додатково Samsung повідомляє про надання 3-нм проєктної інфраструктури та послуг із партнерами SAFE (Samsung Advanced Foundry Ecosystem), включаючи Ansys, Cadence, Siemens та Synopsys. Це має допомогти клієнтам удосконалити свій продукт у найкоротші терміни.